【先进封装助力摩尔定律延续】

摩尔定律主要内容为:在价格不变时,集成电路上可以容纳的晶体管数量每 18-24 个月便会增加一倍,即:处理器性能大约每两年翻一倍,同时价格下降为之前的一半。

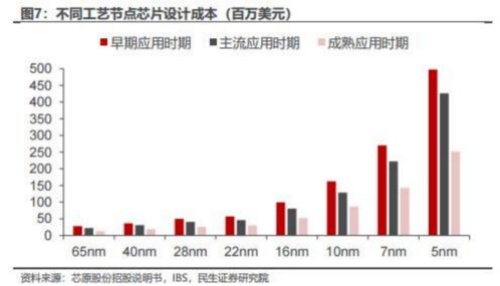

自 2015 年以来,集成电路先进制程的发展开始放缓,7nm、5nm、3nm 制程的量产进度均落后于预期。随着台积电宣布 2nm 制程工艺实现突破,集成电路制程工艺已接近物理尺寸极限;与此同时芯片设计成本快速提升,以先进工艺节点处于主流应用时期设计成本为例,工艺节点为 28nm 时,单颗芯片设计成本约为0.41 亿美元,而工艺节点为 7nm 时设计成本提升至 2.22 亿美元。

为有效降低成本、进一步提升芯片性能、丰富芯片功能,各家龙头厂商争相探索先进封装技术。先进封装技术作为提高连接密度、提高系统集成度与小型化的重要方法,在单芯片向更高端制程推进难度大增时,担负起延续摩尔定律的重任。

如今,除了单个芯片封装形式的演进以外,多芯片集成、2.5D/3D 堆叠等技术也成为现阶段先进封装的主流技术路径,尤其对于大规模集成电路,Chip let封装技术应运而生发挥重要作用。

【先进封装已成 AI 芯片供应瓶颈,扩产蓄势待发】

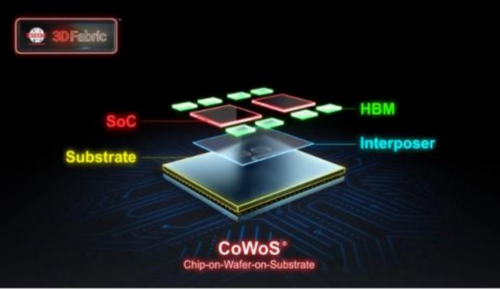

继算力、存力之后,AI 芯片封装的“封力”也已经走到聚光灯下。之前 AIGPU供不应求,主要瓶颈环节就在于CoWoS封装。而在以英伟达为首的 AI 芯片巨头需求推动下,半导体先进封装需求水涨船高,扩产蓄势待发。

据台媒日前援引机构表述称,英伟达6 月下旬起,已开始推动台积电向委外封测代工(OSAT)合作伙伴发送硅中介层载板产能需求,并同步推动联电扩大2024 年硅中介层载板产能。另外,近期 Amkor 和矽品陆续与 CoWoS 设备供应商密集洽谈,很可能意味着将进行扩产。

由于 AI 领域需求增长,英伟达、博通、AMD 争抢台积电 CoWoS 产能。由于英伟达和台积电之前都低估了市场对数据中心 GPU 的需求,现有的封装设备已无法满足,为此后者还紧急订购新的封装设备,预计要将 2.5D 封装产能扩大 40%以上,以满足英伟达不断增长的需求。

据 The Elec 报道,英伟达正在寻求增加 HBM3 与 2.5D 封装供应商,其已与 三星等公司开始展开洽谈。

【Chip let 展现集成优势,市场空间显著】

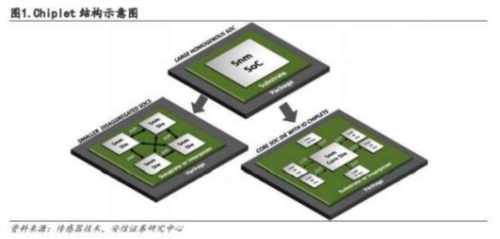

Chip let 俗称“芯粒 ”或“小芯片组 ”,通过将原来集成于同一 SoC 中的各个元件分拆,独立为多个具特定功能的 Chip let,分开制造后再通过先进封装技术将彼此互联,最终集成封装为一个系统芯片。Chip let 可以将一颗大芯片拆解设计成几颗与之有相同制程的小芯片,也可以将其拆解设计成几颗拥有不同制程的小芯片。Chip let 是一种硅片级别的 IP 整合重用技术,其模块化的集成方式可以有效提高芯片的研发速度,降低研发成本和芯片研制门槛。

与传统 SoC 相比,Chip let在设计成本、良率、制造成本、设计灵活性等方面优势明显。

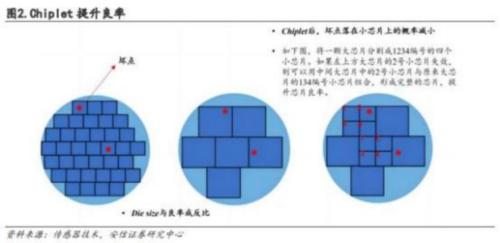

在高性能计算、AI 等方面的巨大运算需求下,芯片性能快速提升,芯片中的晶体管数量也在快速增加,导致芯片面积不断变大。对于晶圆制造工艺而言, 芯片面积越大,工艺的良率越低。通过运用 Chip let 的手段,可以将大芯片拆 解分割成几颗小芯片,单个芯片面积变小,失效点落在单个小芯片上的概率将大大降低,从而提高了制造良率。

由于 Chip let 芯粒可以独立设计和组装,因此制造商可以根据自己的需要来选择不同类型、不同规格和不同供应商的芯粒进行组合,很大程度上提高了芯片设计的灵活性和可定制化程度;并且制造商可以依赖于预定好的芯片工具箱来设计新产品,缩短芯片的上市时间。

2022 年 3 月,英特尔、AMD、Arm、高通、三星、台积电、日月光、Google Cloud、Meta、微软等全球领先的芯片厂商共同成立了UCIe联盟,旨在建立统一的 die-to-die 互联标准,促进 Chip let 模式的应用发展,目前联盟成员已有超过 80 家半导体企业,越来越多的企业开始研发 Chip let 相关产品。UCIe 在解决Chip let 标准化方面具有划时代意义,标志着产业化落地开始。

中国首个原生 Chip let 技术标准《小芯片接口总线技术要求》于 2022 年 12 月发布,该标准有助于行业规范化、标准化发展,为赋能集成电路产业打破先进制程限制因素,提升中国集成电路产业综合竞争力,加速产业进程发展提供指导和支持。

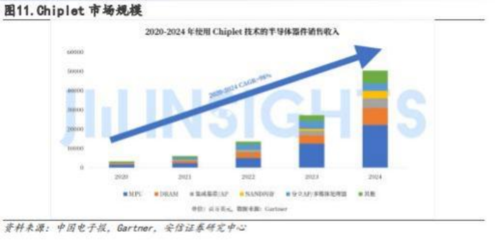

根据 Gartner 数据统计,基于 Chip let 的半导体器件销售收入在 2020 年 仅为 33 亿美元,2022 年已超过 100 亿美元,预计 2023 年将超过 250 亿美元, 2024 年将达到 505 亿美元,复合年增长率高达 98%。超过 30%的 SiP 封装将使用芯粒(Chip let)来优化成本、性能和上市时间。MPU占据 Chip let 大部分应用应用场景,Omdia 预测 2024年用于 MPU 的 Chip let 约占 Chip let 总市场规模的 43%。

【龙头 IC 制造及封测厂加码布局 Chip let】

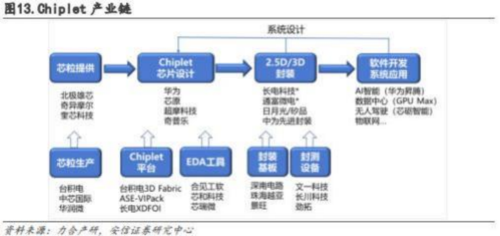

随着 Chip let 技术的发展,Chip let 产业链各环节逐渐完善,即由 Chip let 系统级设计、EDA/IP、芯粒、制造、封测组成的完整Chip let生态链。从 Chip let产业链逻辑看,芯片设计和封装处于链条中心环节,且与后端系统应用紧密联动,而晶圆厂则被前置,成为芯粒提供商的生产环节。

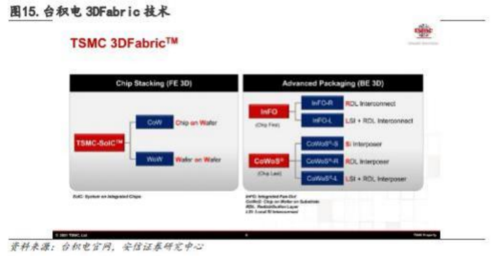

目前全球封装技术主要由台积电、三星、Intel 等公司主导,主要是 2.5和 3D 封装。2.5D封装技术已非常成熟,广泛应用于 FPGA、CPU、GPU 等芯片,目前是 Chip let 架构产品主要的封装解决方案。3D 封装能够帮助实现 3D IC,即晶粒间的堆叠和高密度互连,可以提供更为灵活的设计选择。但3D封装的技术难度更高,目前主要有英特尔和台积电掌握 3D 封装技术并商用。

Chip let 被视为中国与国外差距相对较小的先进封装技术,有望带领中国半导体产业在后摩尔时代实现质的突破,因此,中国半导体企业紧跟产业趋势,纷纷走向 Chip let 研发的道路。中国三大封测企业长电科技、通富微电与华天科技都在积极布局 Chip let 技术, 目前已经具备 Chip let 量产能力。

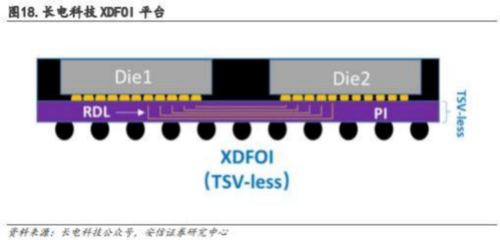

长电科技推出的面 向 Chip let 小芯片的高密度多维异构集成技术平台 XDFOI™可实现TSVless 技术,达到性能和成本的双重优势,重点应用领域为高性能运算如 FPGA、CPU/GPU、AI、5G、 自动驾驶、智能医疗等。

华天科技已量产 Chip let 产品,主要应用于 5G 通信、医疗等领域。华天科技已掌握 SiP、 FC、TSV、Bumping、Fan-Out、WLP、3D 等先进封装技术。华天科技目前已建立三维晶圆级封装平台—3D Matrix,该平台由 TSV、eSiFo(Fan-out)、3D SIP 三大封装技术构成。

参考资料:安信证券-集成电路行业:先进制程贴近物理极限,算力需求 Chip let 迎来黄金发展期-230619.pdf

民生证券-半导体行业深度:算力时代来临,Chip let 先进封装大放异彩-230709.pdf

免责声明:本文由投资顾问 : 冯利勇(执业证书编码:A1280620060001)、何军(执业证书编码:A1280621060001)、罗力川(登记编号:A1280622110002)等编辑整理,仅代表团队观点,任何投资建议不作为您投资的依据,您须独立作出投资决策,风险自担。请您确认自己具有相应的权利能力、行为能力、风险识别能力及风险承受能力,能够独立承担法律责任。所涉及个股仅作投资参考和学习交流,不作为买卖依据。投资有风险,入市需谨慎!